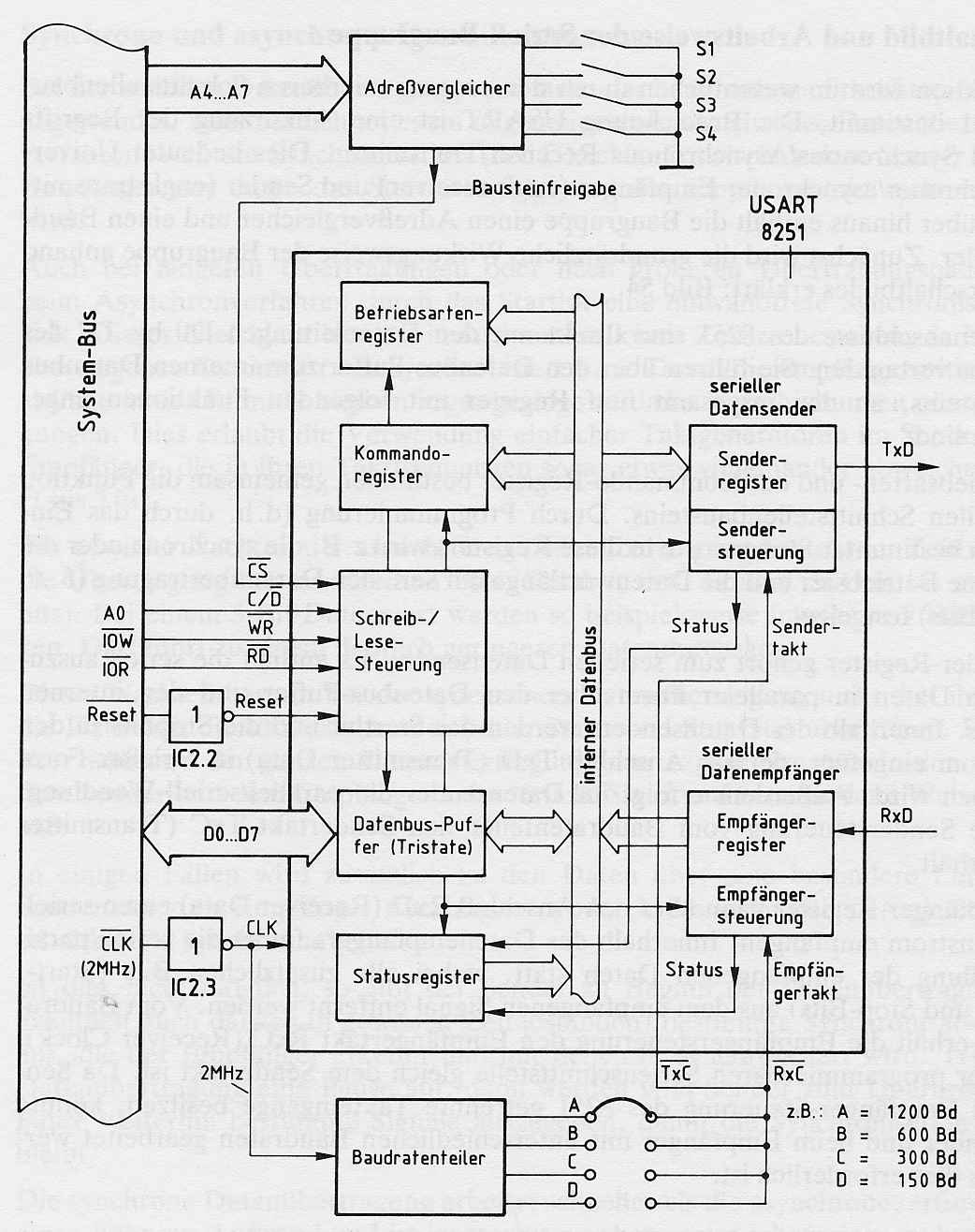

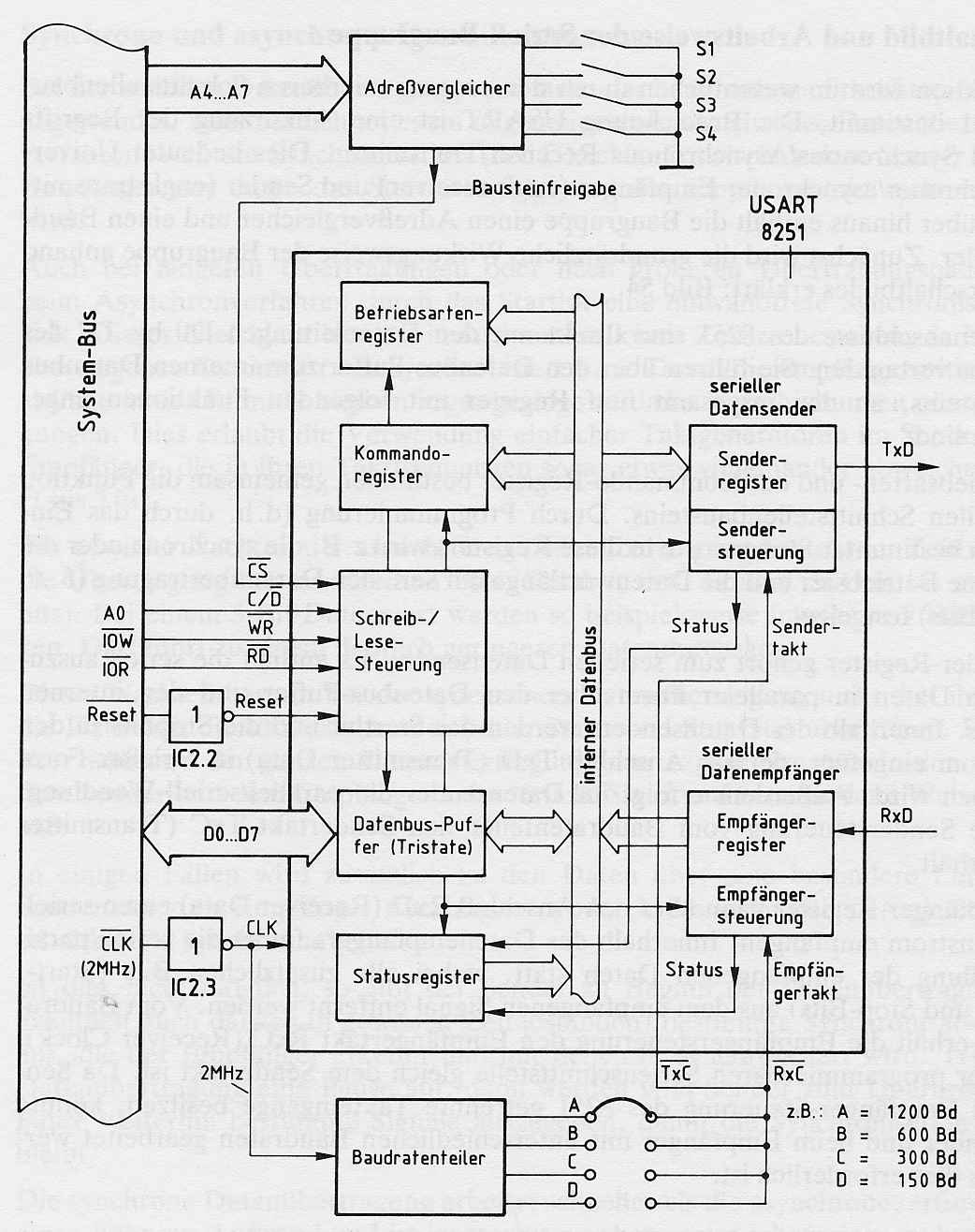

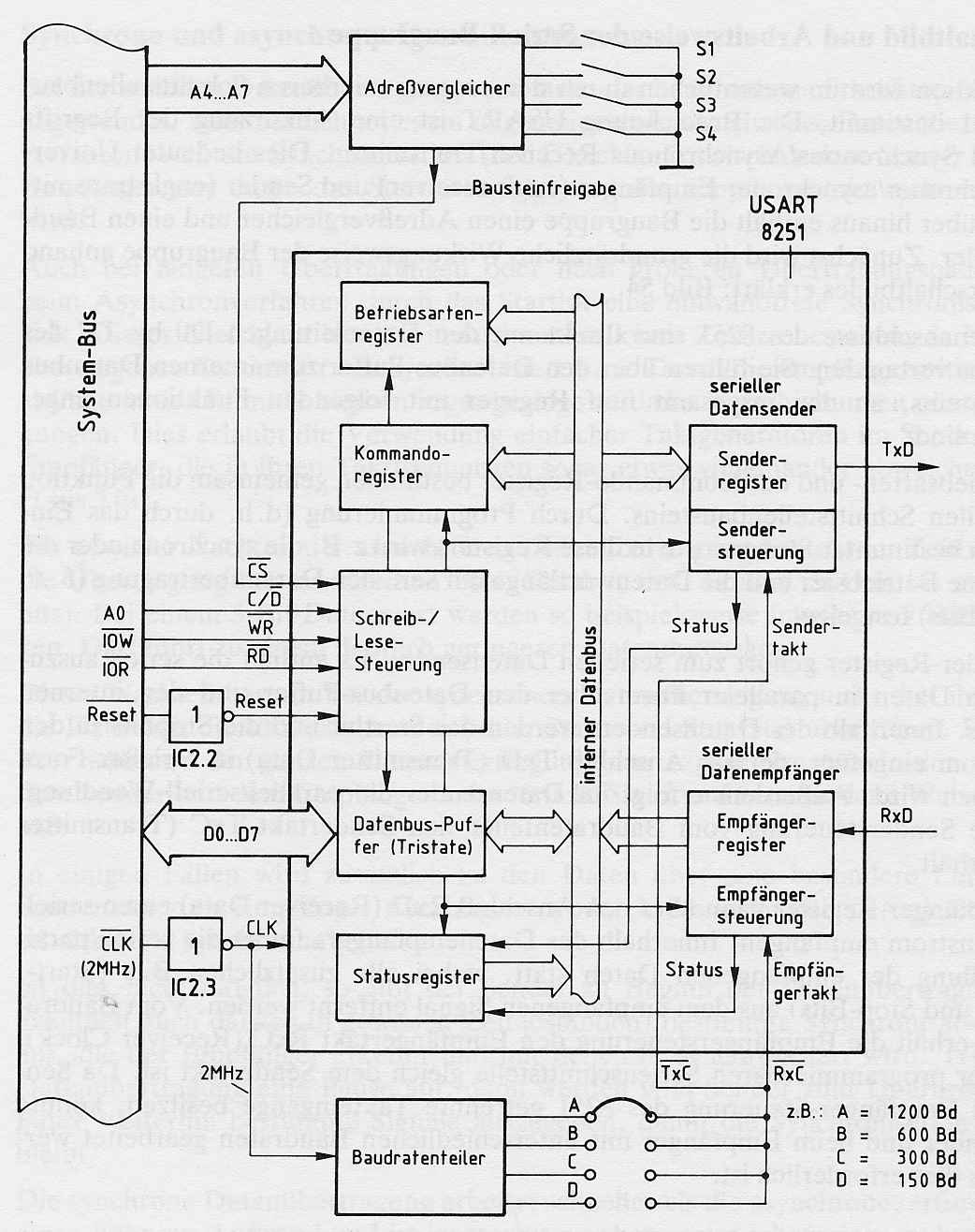

Blockschaltbild und Arbeitsweise der Seriell-Baugruppe

Ihre Funktion wird im wesentlichen durch den programmierbaren Schnittstellenbaustein 8251 bestimmt. Die Bezeichnung USART ist eine Abkürzung des Begriffs Universal Synchronous/Asynchronous Receiver/Transmitter. Dies bedeutet Universaler synchroner/asynchroner Empfänger (engl. receiver) und Sender (engl. transmit-ter). Darüber hinaus enthält die Baugruppe einen Adreßvergleicher und einen Baud-raten-Teiler. Zunächst wird die grundsätzliche Wirkungsweise der Baugruppe anhand des Blockschaltbildes erklärt: Bild 54.

Die Datenanschlüsse des 8251 sind direkt mit den Datenleitungen DO bis D7 des Systembus verbunden. Sie führen über den Datenbus-Puffer zum internen Datenbus des Bausteins, an den insgesamt fünf Register mit folgenden Funktionen angeschlossen sind:

Das Betriebsarten- und das Kommando-Register bestimmen gemeinsam die Funktion des seriellen Schnittstellenbausteins. Durch Programmierung (d.h. durch das Einschreiben bestimmter Steuerworte in diese Register) wird z. B. die synchrone oder die asynchrone Betriebsart und die Datenwortlänge der seriellen Datenübertragung (5, 6, 7 oder 8 Bits) festgelegt.

Das Sender-Register gehört zum seriellen Datensender. Es enthält die seriell auszugebenden Daten in paralleler Form über den Datenbus-Puffer und den internen Datenbus. Innerhalb des Datensenders werden das Startbit und die Stopbits in den Datenstrom eingefügt, der am Anschluß TxD (Transmitter Data) in serieller Form ausgegeben wird. Außerdem erfolgt im Datensender die parallel/seriell-Wandlung, wozu die Sendersteuerung vom Baudratenteiler den Sendertakt TxC (Transmitter Clock) erhält.

Das Empfänger-Register kann über den Anschluß RxD (Receiver Data) einen seriellen Datenstrom empfangen. Innerhalb des Datenempfängers findet die seriell/paral-lel-Wandlung der empfangenen Daten statt, wobei alle zusätzlichen Bits (Start-, Paritäts- und Stop-Bits) aus dem empfangenen Signal entfernt werden. Vorn Baudratenteiler erhält die Empfängersteuerung den Empfängertakt RxC (Receiver Clock), der in der programmierbaren Serienschnittstelle gleich dem Sendertakt ist. Da Sender- und Empfänger-Steuerung des 8251 getrennte Takteingänge besitzen, könnte beim Sender und beim Empfänger mit unterschiedlichen Baudraten gearbeitet werden, falls dies erforderlich ist.

Das Status-Register (Status = Zustand) erhält sowohl vom seriellen Datensender als auch vom seriellen Datenempfänger Informationen über den Zustand dieser Einheiten. Beispiele hierfür sind das Auftreten von Übertragungsfehlern (parity error oder frame error) oder Meldungen wie »Senderregister leer« und »Empfängerregister hat Zeichen empfangen«. Der Prozessor kann das Statusregister lesen und erkennt hierdurch u. a., ob er ein neues Zeichen zur seriellen Ausgabe an die Baugruppe ausgeben kann oder ob ein seriell empfangenes Zeichen vorliegt und eingelesen werden muß.

Damit der serielle Schnittstellenbaustein Daten vom Prozessor erhalten oder an ihn abgeben kann, muß der Anschluß CS (Chip-Select) über die Leitung Bausteinfreigabe ein L-Signal erhalten (Bild 54). Es stammt vom Adreßvergleicher und wird nur abgegeben, wenn die Baugruppe vom Prozessor angesprochen wird, d.h. wenn die Bitkombination der Adreßleitungen A4 bis A7 gleich ist mit der Bitkombination, die mit den Schaltern Sl bis S4 eingestellt wurde (Baugruppennummer).

Die Auswahl der einzelnen Register beim Datenverkehr mit der CPU erfolgt mit Hilfe der Bausteinanschlüsse C/D, WR und RD, auf die später noch weiter eingegangen wird.

Zur zeitlichen Steuerung der internen Vorgänge besitzt der Baustein 8251 die drei Taktanschlüsse RxC, TxC und CLK (Bild 54). RxC und TxC bestimmen die sender-bzw. empfängerseitige Datenübertragungsrate (Baudrate). Hierzu wird der 2-MHz-Systemtakt einem Baudratenteiler zugeführt, der z.B. Baudraten von 1200 Bd, 600 Bd, 300 Bd und 150 Bd ermöglicht.

An CLK ist ein Taktsignal erforderlich, dessen Frequenz wesentlich höher als die höchste Ausgangsfrequenz des Baudratenteilers ist. Hierzu eignet sich der 2-MHz-Sy-stemtakt, der durch IC2.3 invertiert auf den CLK-Anschluß geführt wird. Diese Invertierung soll das CLK-Signal lediglich auffrischen. IC2.2 invertiert das L-aktive Reset-Signal des Systembus, da der Schnittstellenbaustein 8251 einen H-aktiven Re-set-Eingang besitzt. Nach jedem Reset muß der Baustein neu programmiert werden.