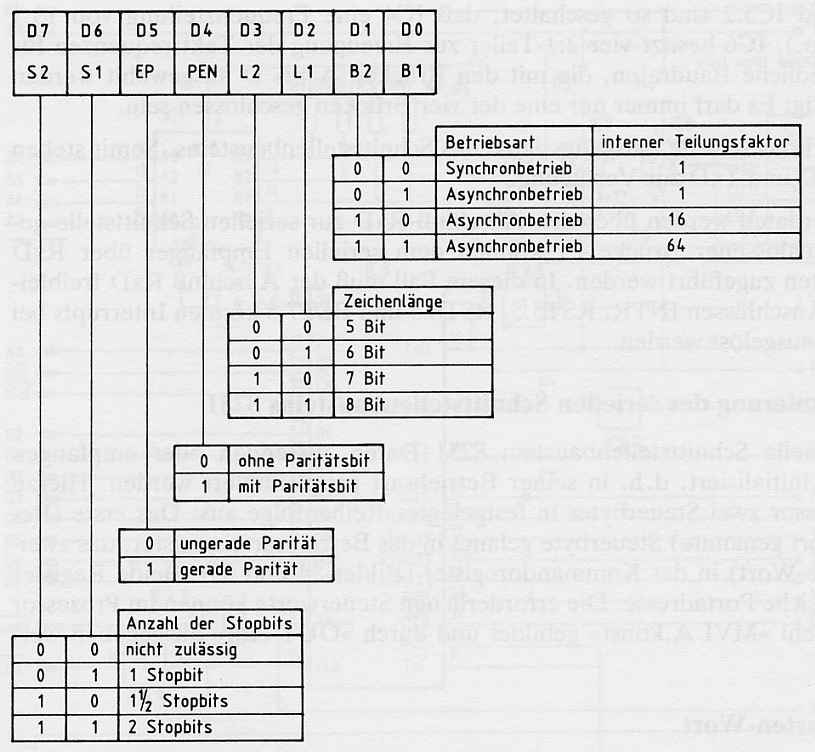

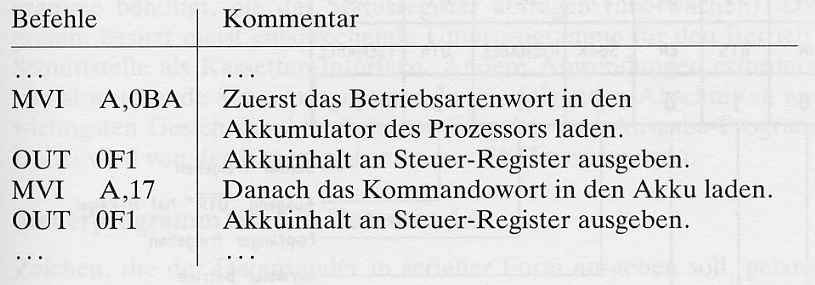

Das Betriebsarten-Wort

Bl (DO) und B2 (Dl), Baudraten- und Betriebsarten-Bits:

Mit Bl und B2 wird die Betriebsart und das interne Teilerverhältnis des seriellen Schnittstellenbausteins festgelegt.

Ll (D2) und L2 (D3), Längen-Bits:

Ll und L2 des Betriebsarten wertes bestimmen die Länge der Datenübertragung, womit die Anzahl der Datenbits innerhalb einer Übertragungssequenz gemeint ist (nicht die Gesamtlänge!). Meist wird eine Übertragung von 7 Bits (z.B. für ASCII-Zeichen) oder 8 Bits (für allgemeine Datenübertragung) gewählt. Eine 5-Bit-Über-tragung ist z.B. für den Baudot-Code (5-Bit-Fernschreib-Code) erforderlich.

PEN (D4), Parity Enable, Paritätsprüfung ein- und ausschalten:

Bei L-Signal (0-Pegel) bildet der Sender kein Paritätsbit. Außerdem prüft der Empfänger nicht die Parität empfangener Zeichen. Bei H-Signal fügt der Sender automatisch Paritätsbits in den Datenstrom ein, und der Empfänger überprüft die Parität der empfangenen Zeichen. Das Ergebnis der Paritätsprüfung steht im Statusregister.

EP (D5), Even Parity, gerade Parität:

Falls das Paritätsbit mit dem Steuerbit PEN (D4) eingeschaltet wurde bzw. eine Paritätsprüfung erfolgen soll, kann mit D5 zwischen der geraden (bei 1-Signal von D5) und der ungeraden Parität (bei 0-Signal) gewählt werden.

Sl (D6) und S2 (D7), Anzahl der Stopbits:

Im Asynchronbetrieb wird hiermit die Anzahl der Stopbits festgelegt. Im Synchronbetrieb haben diese Bits eine andere Bedeutung.

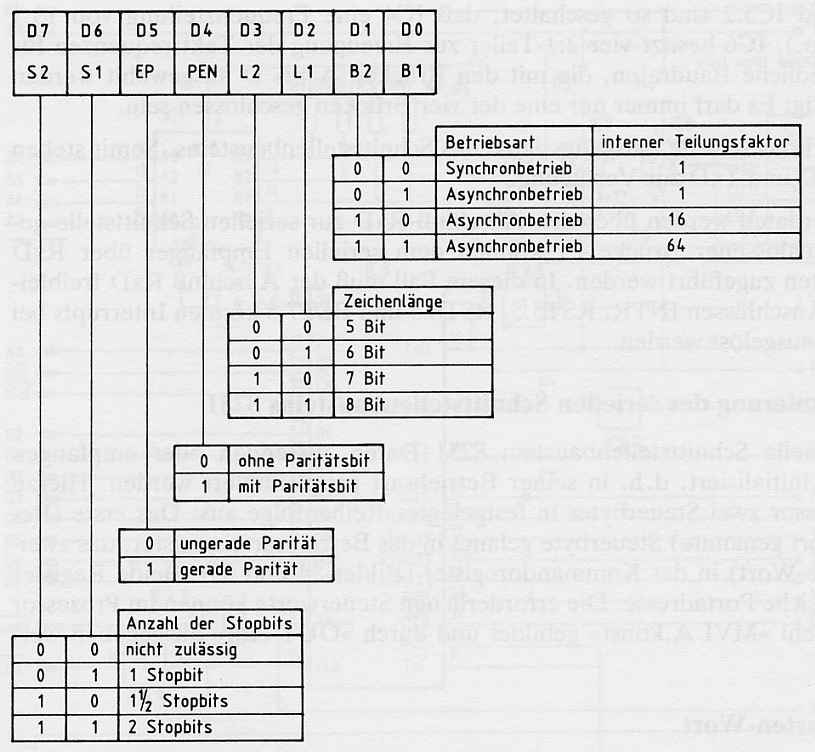

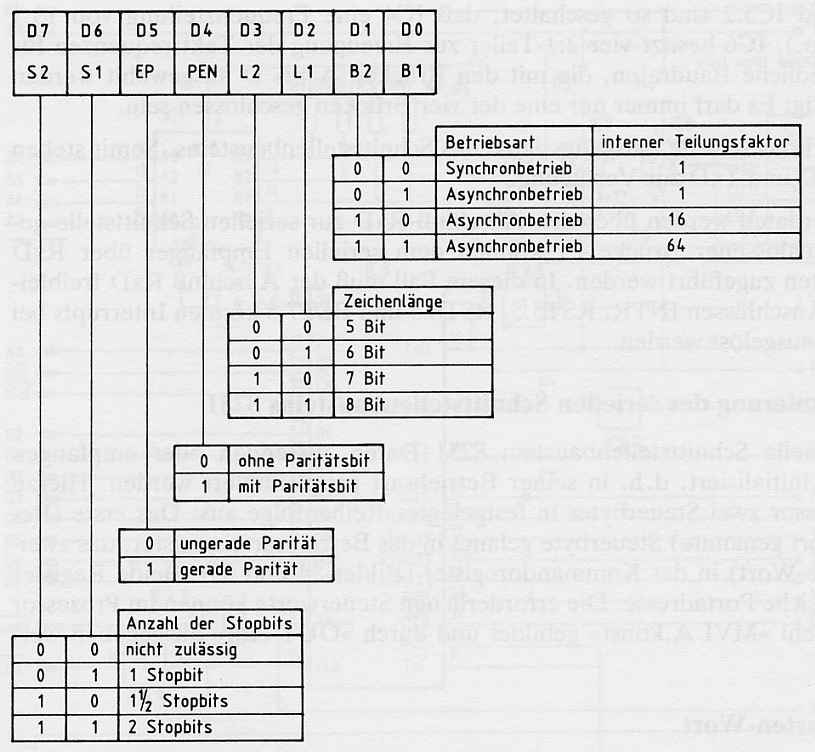

Das Kommando-Wort

Das Kommando-Wort, mit dessen Hilfe mehrere Funktionen gesteuert werden können, gelangt nach der Programmierung des Betriebsartenregisters stets in das Kommandoregister.

Die Bezeichnung und Bedeutung der einzelnen Kommando-Bits:

TxENABLE (DO), Senderfreigabe:

Mit L-Signal wird der serielle Datensender gesperrt und mit H-Signal freigegeben. Zu beachten ist, daß zur Senderfreigabe zusätzlich der Bausteinanschluß CTS L-Pegel führen muß. Die Steuerung des Kommandobits TxENABLE nennt man »Software-Freigabe«; die des Anschlusses CTS heißt Hardware-Freigabe des Senders. Die Senderfreigabe wirkt sich auf den Bausteinanschluß »TxRDY« und das gleichbenannte Bit TxRDY des Statusregisters aus.

Bei freigegebenem Datensender tritt am Schnittstellenausgang TxRDY ein H-Pegel auf, wenn der Datensender bereit ist, ein neues Zeichen aufzunehmen. Ist der Sender jedoch gesperrt, bleibt der Ausgang TxRDY auf L-Pegel, auch wenn der Datensender leer ist und ein Zeichen aufnehmen könnte.

Im allgemeinen wird der Ausgang TxRDY dazu verwendet, einen Prozessor-Interrupt auszulösen, durch den ein neues Zeichen in das Senderregister eingeschrieben wird. Hierbei wirkt die Senderfreigabe so, daß bei H-Signal des Bits TxENABLE das Auftreten des Interrupt-auslösenden H-Signals an TxRDY möglich ist. Bei gesperrtem Sender (Kommando-Bit TxENABLE auf L-Pegel) bleibt TxRDY auf L-Pegel, wodurch kein Interrupt ausgelöst werden kann. Hier wird hiervon allerdings kein Gebrauch gemacht, da die Information, daß der Datensender ein neues Zeichen aufnehmen kann, auch im Bit TxRDY des Statusregisters steht. Falls man ohne Interrupts arbeitet, muß der Prozessor dieses Zustandsbit prüfen, um hierdurch festzustellen, ob der Sender frei ist oder nicht. Bei gesperrtem Sender (Bit TxENABLE des Kommandowortes hat L-Pegel) ist das Statusbit TxRDY ständig auf L-Pegel gesetzt und signalisiert hierdurch, daß der Sender blockiert ist.

DTR (Dl), Ausgang DTR (Data Terminal Ready) setzen:

Dieses Bit des Kommandowortes setzt den beliebig zu verwendenden Bausteinanschluß DTR auf H- oder L-Pegel, wobei für H-Pegel am Ausgang ein L-Pegel des Steuerbits erforderlich ist.

RxENABLE (D2), Empfängerfreigabe:

Mit H-Pegel wird der serielle Datensender freigegeben und mit L-Pegel gesperrt. Das Kommandobit RxENABLE wirkt sich intern auf den Bausteinanschluß RxRDY und auf das gleichbenannte Bit RxRDY des Statusregisters aus.

Bei freigegebenem Empfänger tritt am Schnittstellenausgang RxRDY H-Pegel auf, wenn im Empfängerregister ein Zeichen vorliegt. Führt Bit D2 des Kommandoregisters jedoch L-Pegel, bleibt der Ausgang RxRDY auf L-Pegel, auch wenn Zeichen empfangen wurden.

Im allgemeinen wird der Ausgang RxRDY dazu verwendet, einen Interrupt auszulösen, durch den ein empfangenes Zeichen in den Prozessor eingelesen wird. Hierbei wirkt die Empfängerfreigabe so, daß bei H-Signal des Bits RxENABLE das Auftreten des Interrupt-auslösenden H-Signals an RxRDY möglich ist. Bei gesperrtem Empfänger (Kommando-Bit RxENABLE auf L-Pegel) bleibt RxRDY auf L-Pegel, wodurch kein Interrupt ausgelöst werden kann.

Hier wird hiervon allerdings kein Gebrauch gemacht, da die Information, daß der Empfänger ein neues Zeichen aufgenommen hat, auch im Bit RxRDY des Statusregisters steht. Falls man ohne Interrupts arbeitet, muß der Prozessor dieses Zustandsbit prüfen, um hierdurch festzustellen, ob ein neues Zeichen vorliegt oder nicht. Bei gesperrtem Empfänger (Bit RxENABLE des Kommandowortes hat L-Pegel) ist das Statusbit RxRDY ständig auf L-Pegel gesetzt und signalisiert hierdurch, daß der Empfänger blockiert ist.

SBRK (D3), Send Break (Sende Unterbrechungs-Signal aus):

Dieses Bit wirkt mit dem Bausteinanschluß SYNDET zusammen, der je nach Betriebsart verschiedene Aufgaben besitzt. Informationen hierzu entnehmen Sie bitte den Datenbüchern.

ER (D4), Error Reset (Fehler-Bits des Statusregisters zurücksetzen): Das Statusregister besitzt drei Bits, mit denen das Auftreten bestimmter Fehler bei der Datenübertragung signalisiert wird. Bei H-Signal des Bits ER werden die Fehler-Bits des Statusregisters zurückgesetzt.

RTS (D5), Ausgang RTS (Request To Send) setzen:

Dieses Bit setzt den beliebig zu verwendenden Ausgang RTS auf H- oder L-Pegel, wobei das Steuerbit für H-Pegel am Ausgang L-Pegel besitzen muß.

IR (D6), Initialization Request (Umschalten auf das Betriebsartenregister): Wird dieses Bit auf H-Pegel gesetzt, so gelangt das nächste Steuerwort nicht in das Kommandoregister, sondern in das Betriebsartenregister.

Bei der Initialisierung bzw. Programmierung des Bausteins, zu der nach jedem Kaltstart oder Reset-Signal zwei Steuerworte erforderlich sind, gelangt das erste Steuerwort in das Betriebsartenregister und das zweite, sowie alle folgenden, in das Kommandoregister.

Da es zwei Control-Register (Betriebsarten- und Kommandoregister) gibt, aber zur Unterscheidung zwischen Daten- und Control-Registern nur ein Bausteinanschluß (C/D) vorhanden ist, wurde die Reihenfolge der Programmierung festgelegt. Das Bit IR des Kommando wertes ermöglicht es, nach der Initialisierung, wenn weitere Steuerworte stets in das Kommandoregister gelangen, doch noch, falls nötig, das Betriebsartenregister zu erreichen.

EH (D7), Enter Hunt Mode (Suchen nach Synchronisationszeichen im Synchronbetrieb): Dieses Bit hat im Asynchronbetrieb, auf den sich diese Beschreibung beschränkt, keinen Einfluß.

Das Statusregister

Das Statusregister wird nicht programmiert, sondern kann vom Prozessor nur gelesen werden. Hierdurch erhält er Zustandsmeldungen über den Datensender, den Datenempfänger und einige Bausteinanschlüsse. Außerdem meldet das Statusregister bestimmte Fehler beim seriellen Datenempfang.

Da die Programmierung des Schnittstellenbausteins in gewisser Weise auch das Statusregister beeinflußt, wird es in diesem Zusammenhang behandelt.

Die Bezeichnung und die Bedeutung der einzelnen Status-Bits:

TxRDY (DO), Transmitter Ready (Sender fertig. Besser: Sender bereit zum Empfang des nächsten auszugebenden Zeichens von der CPU):

Dieses Bit des Statusregisters zeigt dem Prozessor durch H-Pegel an, daß das Senderregister leer ist und vom Prozessor ein neues Zeichen aufnehmen kann. Hierdurch wird der Datenaustausch zwischen Mikroprozessor und Schnittstellenbaustein nach dem Abfrage verfahren (Polling-Verfahren) gesteuert, das hier benutzt wird.

Anstelle des Polling-Verfahrens kann die Schnittstelle auch durch Interrupts gesteuert werden. Hierzu ist aber nicht das Statusbit TxRDY, sondern der gleichbenannte Bausteinanschluß TxRDY vorgesehen. Die Funktion des Statusbits TxRDY ist jedoch im Gegensatz zum Bausteinanschluß TxRDY nicht mit dem Bausteinanschluß CTS und dem Kommandobit TxENABLE verknüpft. Weitere Hinweise entnehmen Sie bitte den Datenbüchern.

RxRDY (Dl), Receiver Ready (Empfänger fertig. Besser: Im Empfängerregister liegt ein Zeichen vor, das vom Prozessor gelesen werden kann): Dieses Bit des Statusregisters zeigt dem Prozessor durch H-Pegel an, daß im Empfängerregister ein Zeichen vorliegt, welches vom Prozessor gelesen werden kann. Hierdurch kann der Datenaustausch zwischen Mikroprozessor und Schnittstellenbaustein nach dem Polling-Verfahren gesteuert werden. Das Bit Dl des Statusregisters besitzt die gleiche logische Aussage wie der Bausteinanschluß RxRDY, der zur Interruptsteuerung vorgesehen ist.

TxEMPTY (D2), Transmitter Empty (Datensender leer):

Das Bit D2 des Statusregisters hat H-Pegel, wenn alle Zeichen des seriellen Datensenders (Senderregister und Schieberegister) vollständig ausgegeben wurden. Diese Information entspricht dem logischen Pegel des Bausteinanschlusses TxEMPTY.

PE (D3), Parity Error (Paritätsbit-Fehler):

Bit D3 meldet durch H-Pegel das Auftreten eines Paritätsfehlers, wodurch aber die weitere Arbeitsweise des Empfängers nicht beeinflußt wird. Dieses und die beiden anderen Fehlerbits des Statusregisters können durch ein Kommandowort zurückgesetzt werden.

OE (D4), Overrun Error (Überlauffehler):

Wenn der Prozessor während des seriellen Datenempfangs das Empfängerregister nicht rechtzeitig liest, kann es vorkommen, daß ein Zeichen, das noch im Empfängerregister steht, bereits durch ein neues Zeichen überschrieben wird. In diesem Falle meldet das Bit D4 des Statuswortes einen Überlauf fehler.

FE (D5), Frame Error (Rahmenfehler. Besser: Stopbit-Fehler): Durch das auf der Sender- und der Empfängerseite stets gleiche Übertragungsformat kann der Schnittstellenbaustein das Auftreten des ersten Stopbits vorhersagen. Tritt anstelle des erwarteten H-Signals beim Stopbit ein L-Signal auf, meldet Bit D5 des Steuerregisters dies durch H-Signal.

SYNDET/BD (D6):

Dieses Bit des Statusregisters hat im Synchronbetrieb eine andere Bedeutung als im

Asynchronbetrieb. Es wird hier nicht ausgewertet.

DSR (D7), Data Set Ready, (Betriebsbereitschaft eines [anderen] Gerätes): Der Bausteineingang DSR kann für beliebige Zwecke verwendet werden. Beispielsweise kann ein anderes Gerät dem Prozessor über diesen Anschluß mitteilen, daß es betriebsbereit ist. Führt der Anschluß DSR einen H-Pegel, so besitzt das Statusbit DSR einen L-Pegel (und umgekehrt).

Beispiele zur Programmierung des seriellen Schnittstellenbausteins

Zwei Beispiele sollen die Bildung des Betriebsarten- und Kommandowortes sowie die Programmierung des Bausteins verdeutlichen.

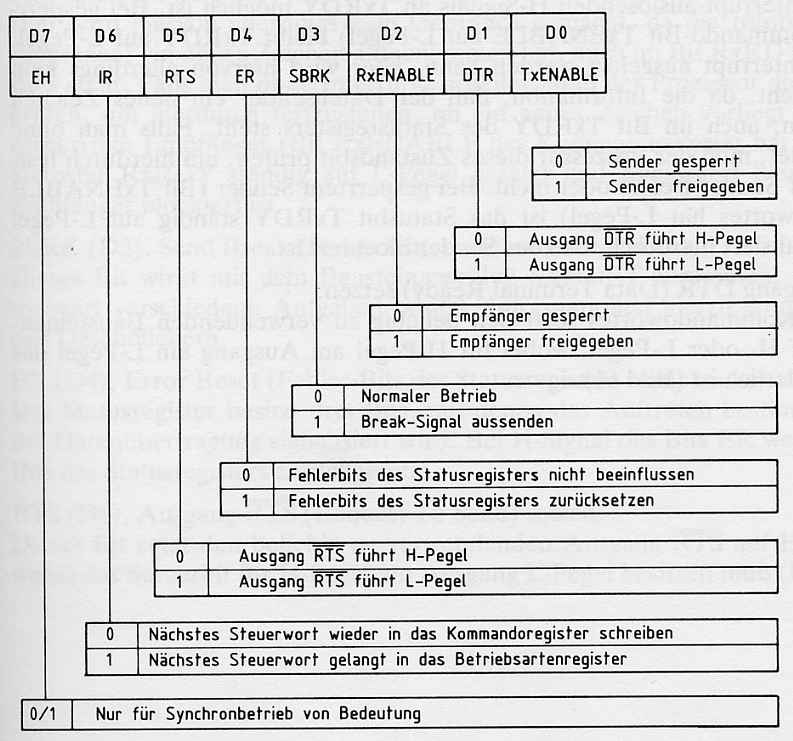

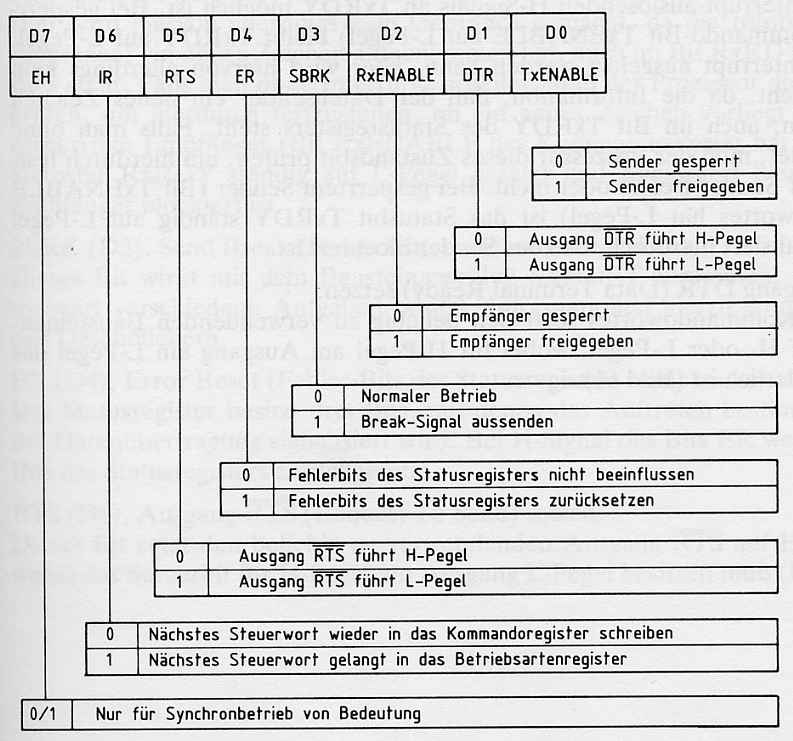

Beispiel 1:

Bei 2400 Bd wird folgende Betriebsart gewünscht:

- Asynchrone Datenübertragung mit einem internen Teilverhältnis von 16:1

- Zeichenlänge 7 Bits

- Paritätsprüfung auf gerade Parität

- l 1/2 Stopbits.

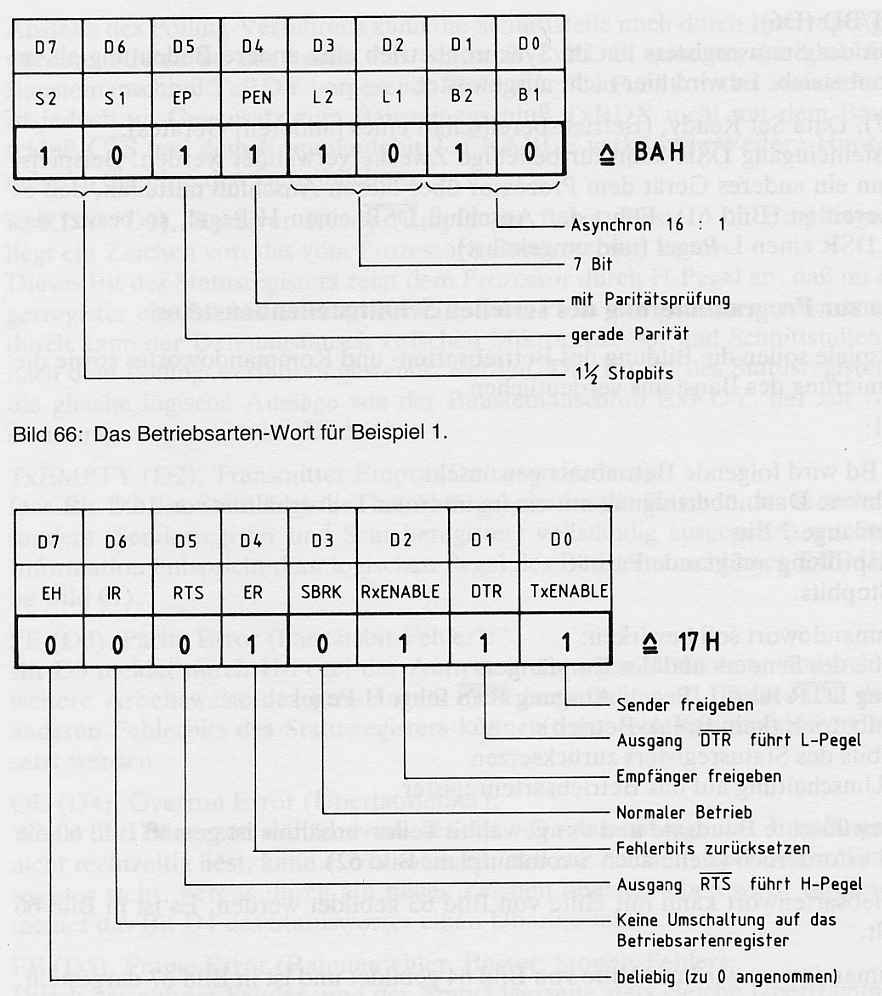

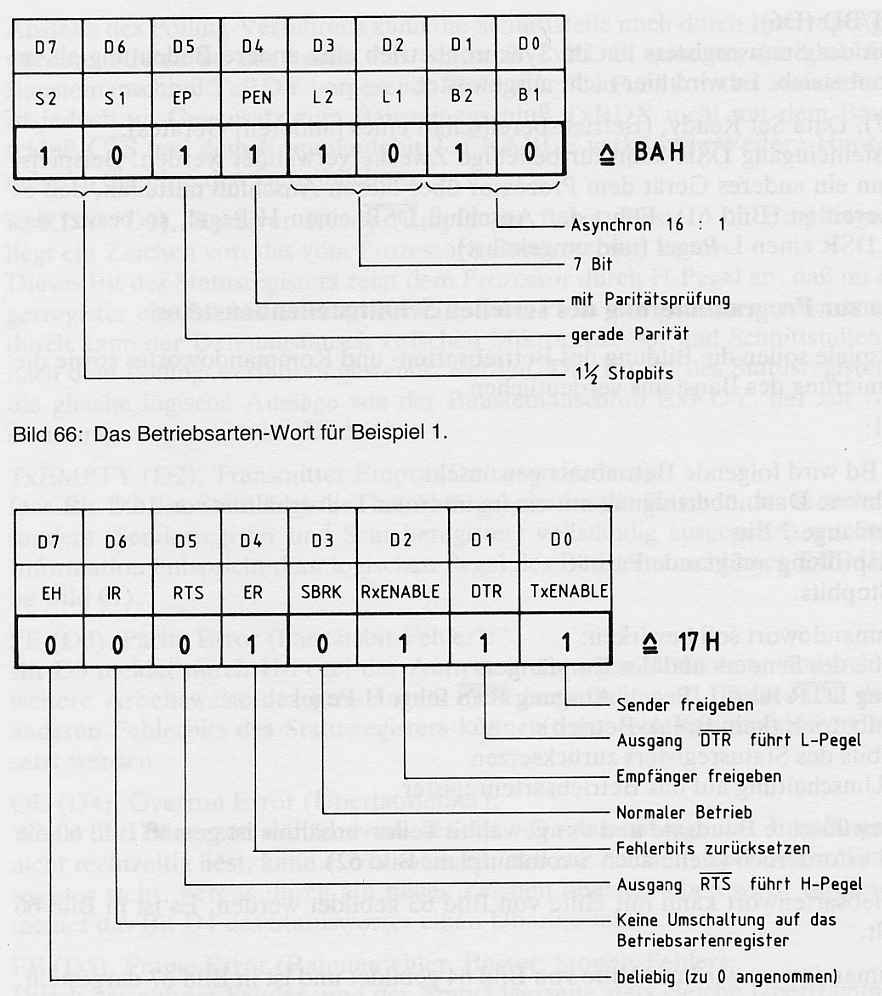

Das Kommandowort soll bewirken:

- Freigabe des Senders und des Empfängers

- Ausgang DTR führt L-Pegel, Ausgang RTS führt H-Pegel

- Normalbetrieb (kein Break-Betrieb)

- Fehlerbits des Statusregisters zurücksetzen

- keine Umschaltung auf das Betriebsartenregister.

Für die gewünschte Baudrate und das gewählte Teilerverhältnis ist die Brücke B erforderlich (siehe auch Stromlaufplan.

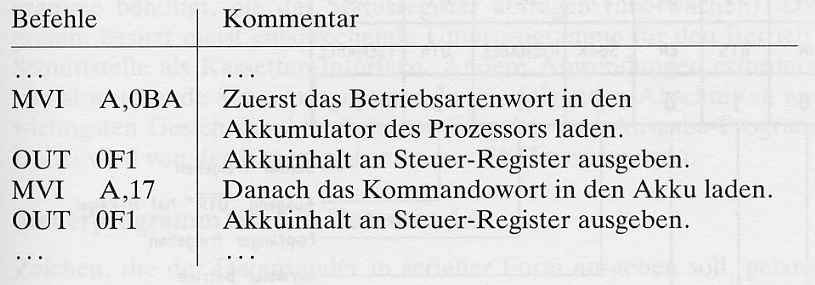

Zur Initialisierung des Schnittstellen-Bausteins müssen die beiden Hex-Werte BA und 17 in die Steuer-Register geschrieben werden. Dabei muß zuerst das Betriebsartenwort und danach das Kommando wort ausgegeben werden. Das folgende Programm, das z.B. Teil des Betriebsprogramms sein kann, initialisiert den Schnittstellenbaustein. Hierbei wird die Baugruppennummer FXH verwendet.

Beispiel 2:

Die programmierbare Serienschnittstelle kann z.B. auch für ein Kassetten-Interface eingesetzt werden. Bei der Initialisierung lautet das Betriebsartenwort dann z.B. CFH, und das Kommando wort ist 25H. Wie ist die Schnittstelle programmiert, wenn die Brücke A des Baudratenteilers verwendet wird?

Das Kassetten-Interface kann durch das Betriebssystem folgendermaßen programmiert werden:

- asynchrone Betriebsart mit internem Teilerfaktor 64:1

- Wortlänge 8 Bits

- keine Paritätsprüfung

- zwei Stopbits

- Sender und Empfänger freigegeben

- Ausgänge: DTR hat H-Pegel, und RTS hat L-Pegel

- Fehlerbits bleiben unbeeinflußt.